Description

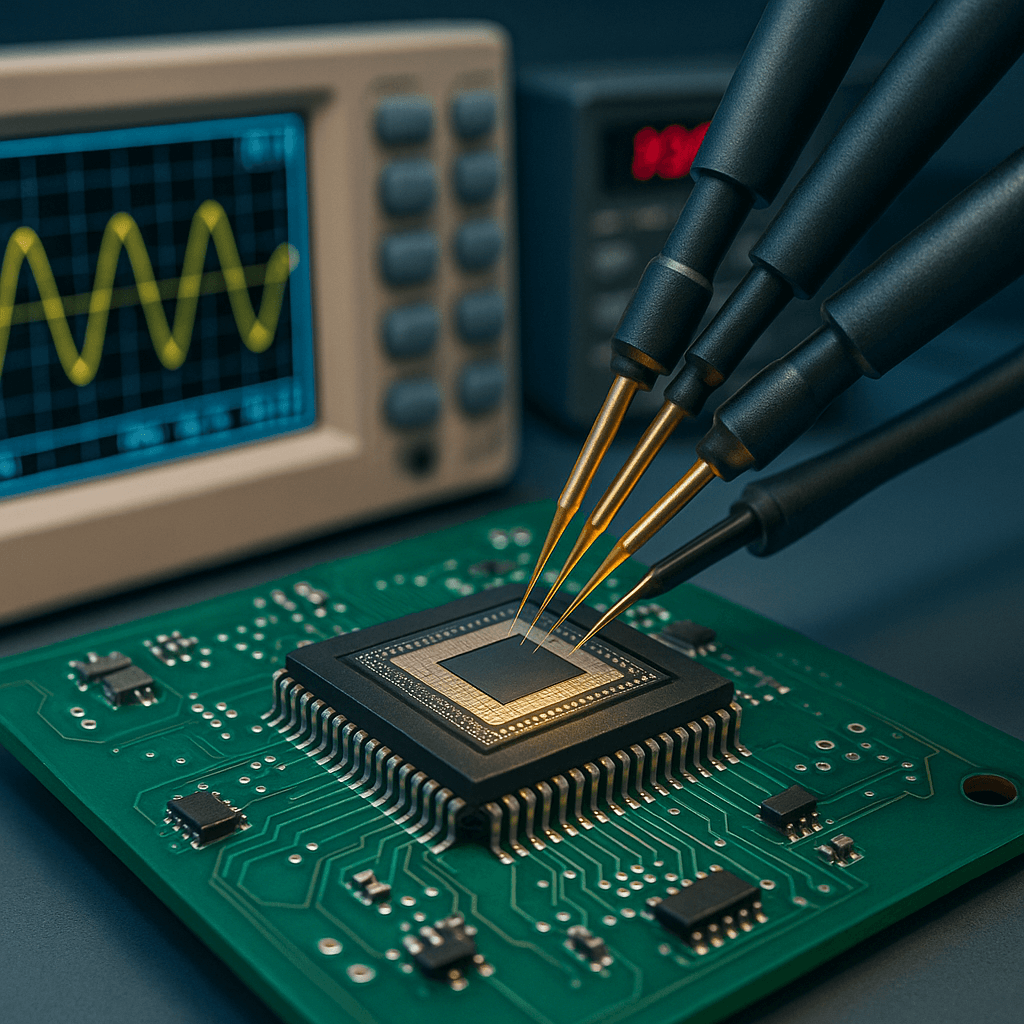

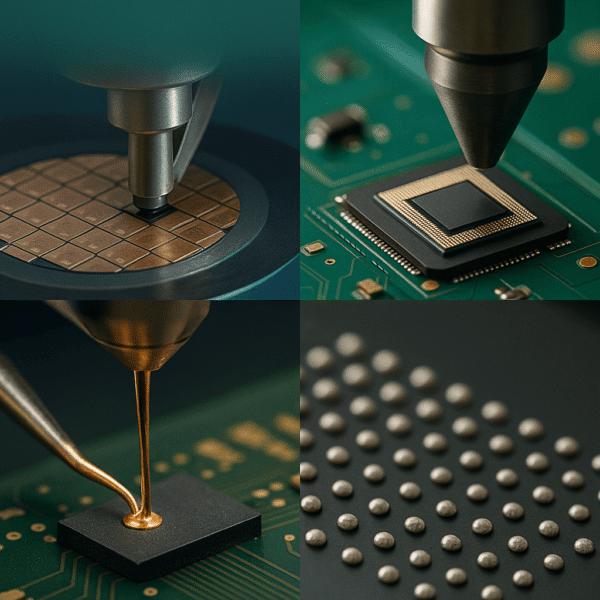

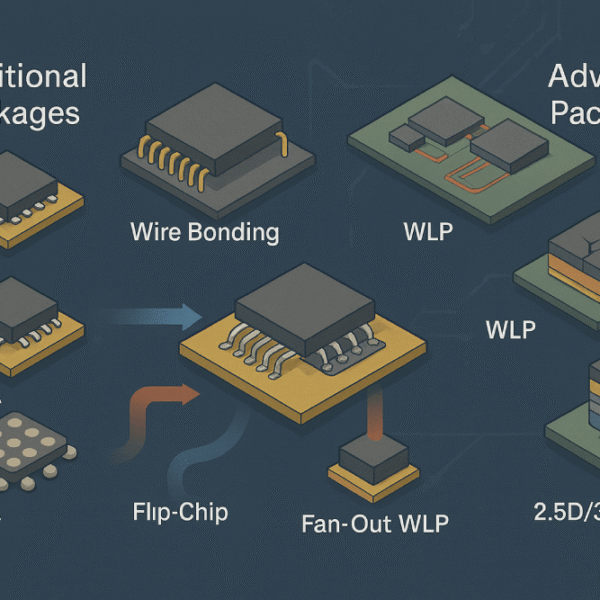

A comprehensive 10-hour course covering the fundamentals, methodologies, and practical considerations of testing semiconductor components and packages. Participants will explore both automated and benchtop testers, key test principles (functional, parametric, boundary-scan, in-circuit, flying-probe), data analysis techniques, design for testability strategies, and best practices in tester calibration and maintenance. Real-world case studies and hands-on examples ensure immediate applicability to reliability, yield enhancement, and quality assurance in semiconductor packaging.

➢ Duration of Modules

| Module | Duration |

| 1. Introduction & Test Fundamentals | 1.0 hour |

| 2. Testing Methodologies, Characteristics, Challenges | 1.5 hours |

| 3. Testers – Automated vs. Benchtop | 1.0 hour |

| 4. Principles of Functional Testing | 1.0 hour |

| 5. Parametric & Boundary-Scan Testing | 1.5 hours |

| 6. In-Circuit Test & Flying Probe Test | 1.5 hours |

| 7. Test Data Analysis | 1.0 hour |

| 8. Design for Testability (DfT) | 1.0 hour |

| 9. Tester Calibration & Maintenance | 0.5 hour |

| 10. Review, Case Studies & Q&A | 0.5 hour |

| Total Duration | 10 hours |

➢ Learning Outcomes

By the end of this course, participants will be able to:

- Articulate the role of component and package testing in semiconductor reliability and yield improvement.

- Distinguish among functional, parametric, boundary-scan, in-circuit, and flying-probe testing methodologies, including their strengths, limitations, and application scenarios.

- Compare automated test equipment (ATE) with benchtop testers and select appropriate test platforms based on throughput, scalability, and cost.

- Develop and validate functional test vectors, define pass/fail criteria, and execute timing-constrained pattern generation.

- Conduct parametric (I–V, C–V) and boundary-scan (JTAG) measurements, interpret results, and troubleshoot scan chain issues.

- Design and implement in-circuit and flying-probe test flows, including fixture design, coverage metrics, and netlist programming.

- Analyze test data using statistical techniques (Cp, Cpk, yield indexing), correlate failures with root causes, and generate actionable dashboards.

- Incorporate Design for Testability (DfT) features—BIST, embedded instrumentation, test pads—into package and PCB layouts without compromising signal integrity.

- Establish calibration and preventive maintenance protocols for testers, ensuring measurement accuracy, documentation, and traceability.

- Apply best practices from real-world case studies to detect packaging defects, optimize yield, and solve participant-specific testing challenges.

➢ Target Audience

This course is ideal for:

- Test engineers and process engineers in semiconductor packaging and assembly.

- Reliability engineers focused on failure analysis and yield enhancement.

- Hardware design engineers seeking to integrate DfT features.

- Quality assurance professionals responsible for test strategy and data analysis.

- Lab technicians and managers evaluating tester procurement and maintenance.

- Graduate students and professionals transitioning into semiconductor test roles.

Reviews

There are no reviews yet.